# **Cryogenic Phase Locking Loop System for** Flux Flow Oscillator

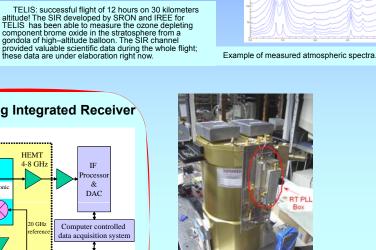

TELIS-MIPAS at Esrange, Sweden; March 2009

Andrey Khudchenko<sup>1</sup>, Valery Koshelets<sup>1</sup>, Pavel Dmitriev<sup>1</sup>, Andrey Ermakov<sup>1</sup>, Oleksandr Pylypenko<sup>2</sup>

FFO Frequency,

GHz

495 04

496.88

505.6

507.28

515 25

519.25

607.78

619 1

Frequencies and subst

H<sub>2</sub>-18O

HDO

CIO

BrO (∆T = 0.3 K !!)

O<sub>2</sub> /pointing /pressure

BrO (ΔT = 0.3 K !!)

HCI (HOCI, CIO)

O<sub>3</sub> isotopes

Substances

(High priority)

<sup>1</sup>Institute of Radio Engineering and Electronics, IREE, Russia <sup>2</sup>State Research Center of Superconducting Electronics "Iceberg", Ukraine

##

1

2

3

4

5

6

7

8

TELIS

#### Abstract

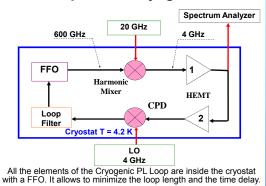

A bandwidth of the typical Phase Locking Loop (PLL) system for the Superconducting Integrated Receiver (SIR) is limited by unavoidable delays in the long cables between SIR inside cryostat semiconductor PLL system outside it. To overcome this limitation we propose Cryogenic Phase Locking Loop (CPLL). The CPLL has been developed for phase locking of a Flux-Flow Oscillator (FFO) in the SIR. The main element of the CPLL is a cryogenic phase detector (CPD) based on a superconductor - insulator - superconductor (SIS) tunnel junction.

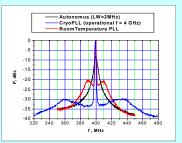

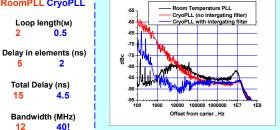

All the loop elements are placed at 4.2 K inside a cryostat with the FFO; so the novel CPLL system has a loop length only 50 cm. The CPLL operating frequency has been increased from 400 MHz up to 4 GHz to decrease a loop filter delay to 0.5 ns. As a result the total loop group delay is about 4.5 ns. Such a small delay results in a CPLL synchronization bandwidth as wide as 40 MHz and allows to phase-lock more than 60% of the emitted by FFO power even for FFO linewidth about 11 MHz. This fraction of phase-locked power is three times large than can be achieved with conventional room-temperature PLL. We have realized an integrating loop filter for the CPLL. Such a filter sufficiently increase stability and decrease a phase noise of the FFO phase-locked by the CPLL.

## Ultrawideband PLL is required (>50 MHz):

For the future SIR applications (f>1THz) an FFO with the NbN electrodes will be used; the FFO linewidth could considerably exceed 10 MHz.

The specification for a ALMA interferometer require a phase stability better then 75 fs. To realize such a stability for the SIR a part of phase locked FFO power – Spectral Ratio (SR), as high as 90% is needed.

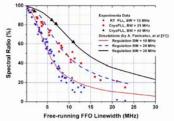

Dependence of the SR vs FFO linewidth for different PLL bandwidths.

The PLL bandwidth is determined by a total group delay in the loop. A bandwidth of the typical PLL system for the SIR is limited by unavoidable delays in the long cables between the SIR inside a cryostat and semiconductor PLL system outside it. To overcome this limitation we propose the CPLL

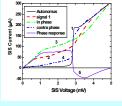

#### SIS - Cryogenic Phase Detector for the CPLL

120 180 240 300 Phase Differnce

CPD based on SIS demonstrates sinusoidal response in dependence on phase difference between two

incoming microwave signals.

I-VCs of a SIS junction. Microwave signals (5 GHz) are applied.

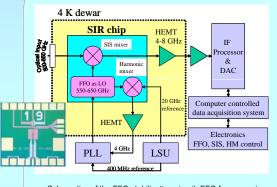

Superconducting Integrated Receiver

Schematics of the FFO stabilization circuit. FFO frequency is mixed in HM with the 19-21 GHz reference. The mixing product is amplified, downconverted and compared with the 400 MHz reference in the PLL. The phase difference signal generated by PLL is used to feedback the FFO control line.

#### Concept of the Cryogenic PLL

**CPLL Loop Elements:** FFO with HM in shield HEMT amplifiers CPD and Loop filter in the box

Loop length is 0.5m.

Photo of the CPLL in cryostat. FFO and CPD are placed in two separated shields.

15

12

Downconverted spectra of FFO. Demonstration of the CPLL advantage: bandwidth = 40 MHz it gives SR = 95% for 2 MHz linewidth compare to SR=82% for the Room Temperature PLL system.

Phase noise of the FFO phase-locked with: "1" –RT PLL; "2" – CPLL without integrating loop filter, "3" - CPLL with integrating loop filter. The CPLL demonstrate a Phase Noise lower then for the Room Temperature PLL at frequencies more then 1KHz.

### Summary

> A new and successful application of a SIS junction - cryogenic phase detector (CPD).

> The CPD intrinsically could operate with an effective bandwidth more than 100 MHz. The maximal output bandwidth more than signal is about 0.1 mV.

> Concept of the CryoPLL system has been proven. Bandwidth as wide as 40 MHz has been obtained.

The improvement of the phase locked FFO spectral ratio from 20% to more than 60% has been achieved at application of the CryoPLL for FFO linewidth 11 MHz.

> CryoPLL has an integrating filter for active phase-locking, stabilization and low phase level noise.